AI-driven applied sciences are weaving themselves into the material of our every day routines, with the potential to reinforce our entry to data and enhance our total productiveness. The spine of those purposes lies in massive language fashions (LLMs). LLMs are memory-intensive and usually require specialised {hardware} accelerators to effectively ship tens of exaflops of computing energy. This weblog publish exhibits how we are able to begin addressing the computational challenges by using reminiscence extra successfully.

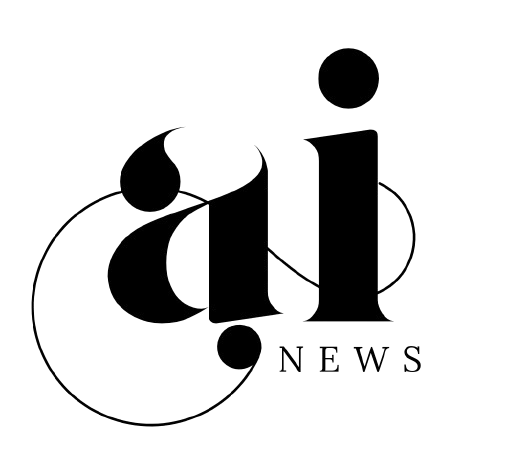

The majority of an LLM’s reminiscence and compute are consumed by weights in matrix multiplication operations. Utilizing narrower information sorts reduces reminiscence consumption. For instance, storing weights within the 8-bit integer (i.e., U8 or S8) information sort reduces the reminiscence footprint by 4× relative to single-precision (F32) and a pair of× relative to half-precision (F16) or bfloat16 (BF16). Moreover, earlier work has proven that LLM fashions operating matrix multiplications with weights in S8 and enter in F16 (preserving increased precision of the user-input) is an efficient methodology for rising the effectivity with acceptable trade-offs in accuracy. This method is called weight-only quantization and requires environment friendly implementation of matrix multiplication with mixed-inputs, e.g., half-precision enter multiplied with 8-bits integer. {Hardware} accelerators, together with GPUs, help a hard and fast set of information sorts, and thus, mixed-input matrix multiplication requires software program transformations to map to the {hardware} operations.

To that finish, on this weblog we concentrate on mapping mixed-input matrix multiplication onto the NVIDIA Ampere structure. We current software program strategies addressing information sort conversion and format conformance to map mixed-input matrix multiplication effectively onto hardware-supported information sorts and layouts. Our outcomes present that the overhead of further work in software program is minimal and permits efficiency near the height {hardware} capabilities. The software program strategies described listed here are launched within the open-source NVIDIA/CUTLASS repository.

|

| Reminiscence footprint for an 175B parameter LLM mannequin with numerous information sorts codecs. |

The matrix-multiply-accumulate operation

Trendy AI {hardware} accelerators equivalent to Google’s TPU and NVIDIA’s GPU multiply matrices natively within the {hardware} by focusing on Tensor Cores, that are specialised processing parts to speed up matrix operations, notably for AI workloads. On this weblog, we concentrate on NVIDIA Ampere Tensor Cores, which give the matrix-multiply-accumulate (mma) operation. For the remainder of the weblog the reference to mma is for Ampere Tensor Cores. The supported information sorts, shapes, and information format of the 2 enter matrices (known as operands) for the mma operation are mounted in {hardware}. Because of this matrix multiplications with numerous information sorts and bigger shapes are applied within the software program by tiling the issue onto hardware-supported information sorts, shapes, and layouts.

The Tensor Core mma operation is outlined by specifying two enter matrices (e.g., A & B, proven beneath) to provide a end result matrix, C. The mma operation natively helps mixed-precision. Blended-precision Tensor Cores permit mixing enter (A and B) information sort with the end result (C) information sort. In distinction, mixed-input matrix multiplication includes mixing the enter information sorts, and it’s not supported by the {hardware}, so it must be applied within the software program.

|

| Tensor Core operation of M-by-N-by-Ok on enter matrix A of M-by-Ok and matrix B of Ok-by-N produces output matrix C of M-by-N. |

Challenges of mixed-input matrix multiplication

To simplify the dialogue, we prohibit to a selected instance of mixed-input matrix multiplication: F16 for consumer enter and U8 for the mannequin weights (written as F16 * U8). The strategies described right here work for numerous mixtures of mixed-input information sorts.

A GPU programmer can entry a hierarchy of reminiscence, together with world reminiscence, shared reminiscence, and registers, that are organized so as of lowering capability however rising velocity. NVIDIA Ampere Tensor Core mma operations devour enter matrices from registers. Moreover, enter and output matrices are required to adapt to a format of information inside a gaggle of 32 threads often called a warp. The supported information sort and format inside a warp are mounted for an mma operation, so to implement mixed-input multiplication effectively, it’s mandatory to resolve the challenges of information sort conversion and format conformance in software program.

Information sort conversion

The mma operation requires two enter matrices with the identical information sort. Thus, mixed-input matrix multiplication, the place one of many operands is saved in U8 in world reminiscence and different in F16, requires an information sort conversion from U8 to F16. The conversion will deliver two operands to F16, mapping the mixed-input matrix multiplication to hardware-supported mixed-precision Tensor Cores. Given the massive variety of weights, there are a lot of such operations, and our strategies present methods to cut back their latency and enhance efficiency.

Format conformance

The mma operation additionally requires the format of two enter matrices, throughout the registers of a warp, to be conformat with {hardware} specification. The format for the enter matrix B of U8 information sort in mixed-input matrix multiplication (F16 * U8) wants to adapt with the transformed F16 information sort. That is known as format conformance and must be achieved within the software program.

The determine beneath exhibits an mma operation consuming matrix A and matrix B from registers to provide matrix C in registers, distributed throughout one warp. The thread T0 is highlighted and zoomed in to indicate the burden matrix B goes by way of information sort conversion and desires a format conformance to have the ability to map to the hardware-supported Tensor Core operation.

Software program methods addressing challenges

A typical information sort conversion includes a sequence of operations on 32-bit registers, proven beneath. Every rectangular block represents a register and the adjoining textual content are the operations. All the sequence exhibits the conversion from 4xU8 to 2x(2xF16). The sequence includes roughly 10 operations.

There are lots of methods of attaining format conformance. Two of the present options are:

- Narrower bitwidth shared reminiscence hundreds: On this method, threads subject slim bitwidth reminiscence hundreds transferring the U8 information from shared reminiscence to registers. This ends in two 32-bit registers, with every register containing 2xF16 values (proven above for the matrix B’s thread T0). The narrower shared reminiscence load achieves format conformance straight into registers with no need any shuffles; nonetheless, it doesn’t make the most of the complete shared reminiscence bandwidth.

- Pre-processing in world reminiscence: An different technique includes rearranging the information throughout the world reminiscence (one degree above the shared reminiscence in reminiscence hierarchy), permitting wider shared reminiscence hundreds. This method maximizes the shared reminiscence bandwidth utilization and ensures that the information is loaded in a conformant format straight within the registers. Though the rearrangement course of may be executed offline previous to the LLM deployment, guaranteeing no influence on the applying efficiency, it introduces an extra, non-trivial hardware-specific pre-processing step that requires an additional program to rearrange the information. NVIDIA/FasterTransformer adopts this methodology to successfully tackle format conformance challenges.

Optimized software program methods

To additional optimize and cut back the overhead of information sort conversion and format conformance, we now have applied FastNumericArrayConvertor and FragmentShuffler, respectively.

FastNumericArrayConvertor operates on 4xU8 in 32-bit registers with out unpacking particular person 1xU8 values. Moreover, it makes use of cheaper arithmetic operations which reduces the variety of directions and will increase the velocity of the conversion.

The conversion sequence for U8-to-F16 is proven beneath. The operations use packed 32b registers, avoiding express unpacking and packing. FastNumericArrayConvertor makes use of the permute byte to rearrange bytes of 4xU8 into two registers. Moreover, FastNumericArrayConvertor doesn’t use costly integer to floating-point conversion directions and employs vectorized operations to acquire the packed ends in two 32-bit registers containing 2x(2xF16) values. The FastNumericArrayConvertor for U8-to-F16 roughly makes use of six operations, a 1.6× discount relative to the method proven above.

|

FastNumericArrayConvertor makes use of permute bytes and packed arithmetic, lowering the variety of directions within the information sort conversion. |

FragmentShuffler handles the format conformance by shuffling information in a means that permits using wider bitwidth load operation, rising shared reminiscence bandwidth utilization and lowering the overall variety of operations.

NVIDIA Ampere structure gives a load matrix instruction (ldmatrix). The ldmatrix is a warp-level operation, the place 32 threads of a warp transfer the information from shared reminiscence to registers within the form and format that mma matrix A and B devour. The usage of ldmatrix reduces the variety of load directions and will increase the reminiscence bandwidth utilization. Because the ldmatrix instruction strikes U8 information to registers, the format after the load conforms with U8*U8 mma operation, and never with F16*F16 mma operation. We applied FragmentShuffler to rearrange the information inside registers utilizing shuffle (shfl.sync) operations to attain the format conformance.

Essentially the most vital contribution of this work is to attain format conformance by way of register shuffles, avoiding offline pre-processing in world reminiscence or narrower bitwidth shared reminiscence hundreds. Moreover, we offer implementations for FastNumericArrayConvertor protecting information sort conversion from U8-to-F16, S8-to-F16, U8-to-BF16, and S8-to-BF16.

Efficiency outcomes

We measured the efficiency of eight mixed-input variants of our methodology (proven beneath in blue and crimson; various the information kinds of matrix A and B) and two mixed-precision information sorts (proven in inexperienced) on an NVIDIA A100 SXM chip. The efficiency outcomes are proven in FLOPS (increased is best). Notably, the primary eight matrix-multipications require further operations relative to the final two, as a result of the mixed-precision variants straight goal hardware-accelerated Tensor Core operations and don’t want information sort conversion and format conformance. Even so, our method demonstrates mixed-input matrix multiplication efficiency solely barely beneath or on par with mixed-precision.

|

Blended-input matrix multiplication efficiency on NVIDIA A100 40GB SMX4 chip for a compute-bound matrix drawback form m=3456, n=4096, okay=2048. |

Acknowledgements

We want to point out a number of people who’ve contributed by way of technical brainstorming and enhancing the weblog publish together with, Quentin Colombet, Jacques Pienaar, Allie Culp, Calin Cascaval, Ashish Gondimalla, Matt Walsh, Marek Kolodziej, and Aman Bhatia. We want to thank our NVIDIA companions Rawn Henry, Pradeep Ramani, Vijay Thakkar, Haicheng Wu, Andrew Kerr, Matthew Properly, and Vartika Singh.